In digital systems, timing analysis is the practice of determining the maximum clock frequency (minimum clock period) for which a circuit will operate properly, and determine if the circuit suffers from any timing violations.

Two main categories involve timing for combinational circuits (propagation delay for gates) and for sequential circuits (set-up and hold time for latches, flip-flops). Memory also comes with its own set of considerations.

Big ideas

The path of longest delay is called the critical path, which is usually the path with the most gates we pass through (but not always).

Sequential calculations

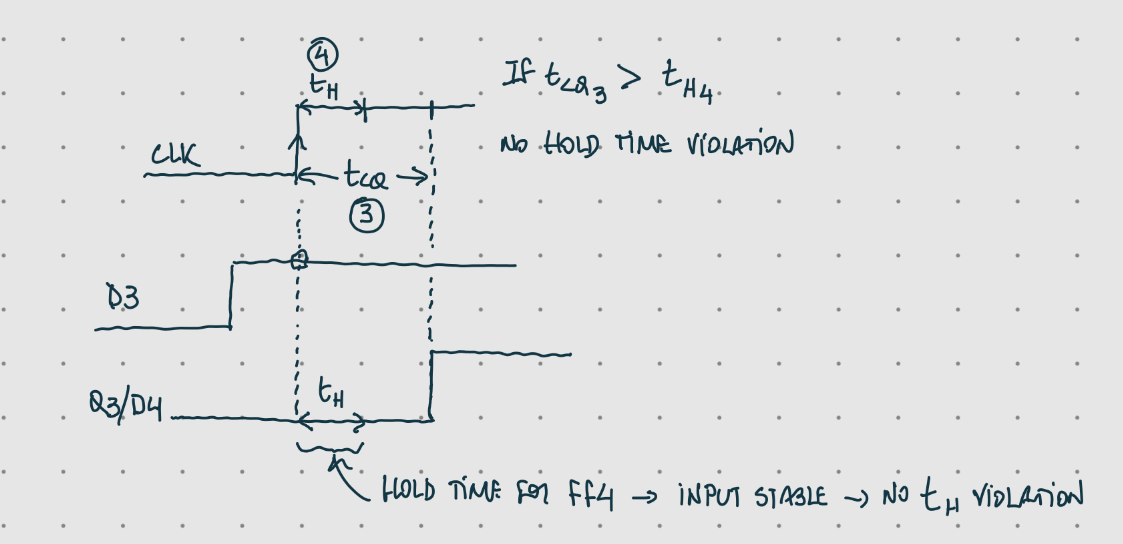

This is especially relevant for considering flip-flops. We define two parameters:

- is the time delay between the clock edge and the change of the Q output.

- is the amount of time the input must be stable before the clock edge.

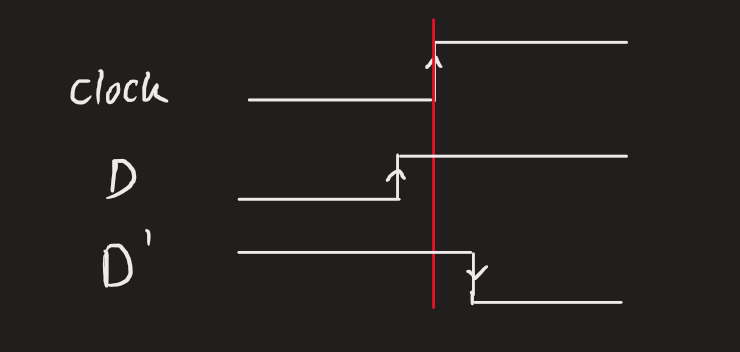

- is the amount of time must be stable after the clock edge.

should not change in the time window around the rising clock edge. We can calculate, first by finding the minimum clock period:

We want to do the calculations for the critical path, then to find the maximum frequency we can find the inverse of .

We say that there’s no hold-time violation if:

Hold-time calculations are done with the shortest path.

We can avoid or change the nature of timing violations with clock skews.

We can avoid or change the nature of timing violations with clock skews.

Implications

If the circuit doesn’t meet or honour the setup time, the flip-flop may go “metastable”, where it oscillates or otherwise has unpredictable results. For instance, for a quick change in , we may not store values in the flip-flop as intended.