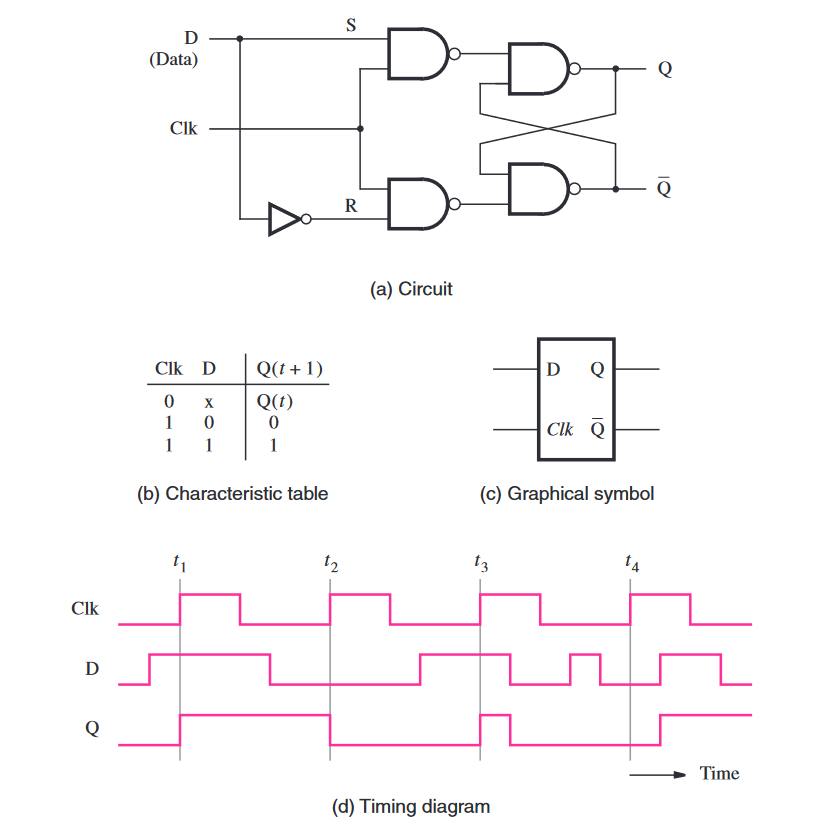

Gated D-latches are sequential circuits with memory elements (i.e., they remember some value). They are designed to prevent the possibility of oscillations that are prevalent in RS latches.

D-latches are used within flip-flops, a common storage element in modern digital circuit design.

Foundations

When the clock is 0, and stay in their previous state (and store some value). When the clock is 1, then and , i.e., they only change value when the clock turns on. Since the output of the latch is dictated by the level of the clock, the latch is level sensitive.

See how the above property is true in the timing diagram below!

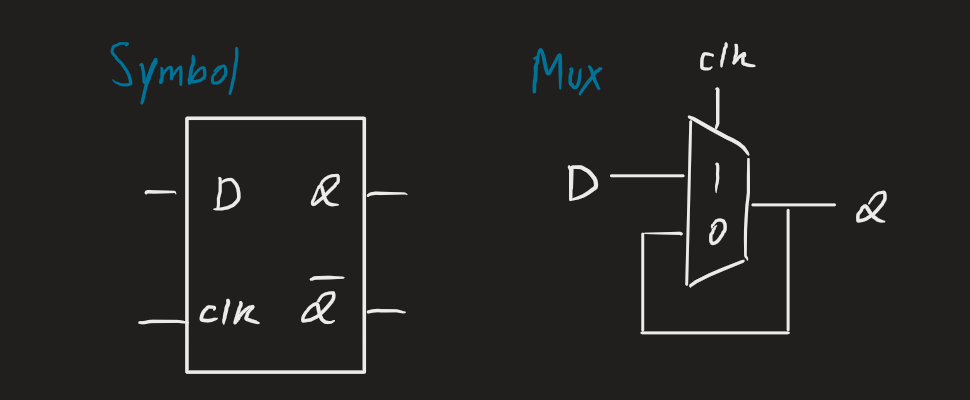

We can also implement using a mux.

We can also implement using a mux.

HDL implementation

Notice that there’s no else statement in the implementation. The way the Verilog compiler interprets it is that Q will hold its previous state.

module d_latch(D, clock, Q);

input D, clock;

output reg Q;

always @(D, clock)

begin

if (clock == 1'b1)

Q = D;

end

endmodule