SR latches (for set-reset) are a broad category of sequential circuit involving cross-coupled NOR gates. Gated latches introduce the addition of a control element, often called a clock.

SR latches form an easy introduction to other circuits with memory elements, like D-latches and flip-flops. In modern digital circuit design, SR latches are rarely used.

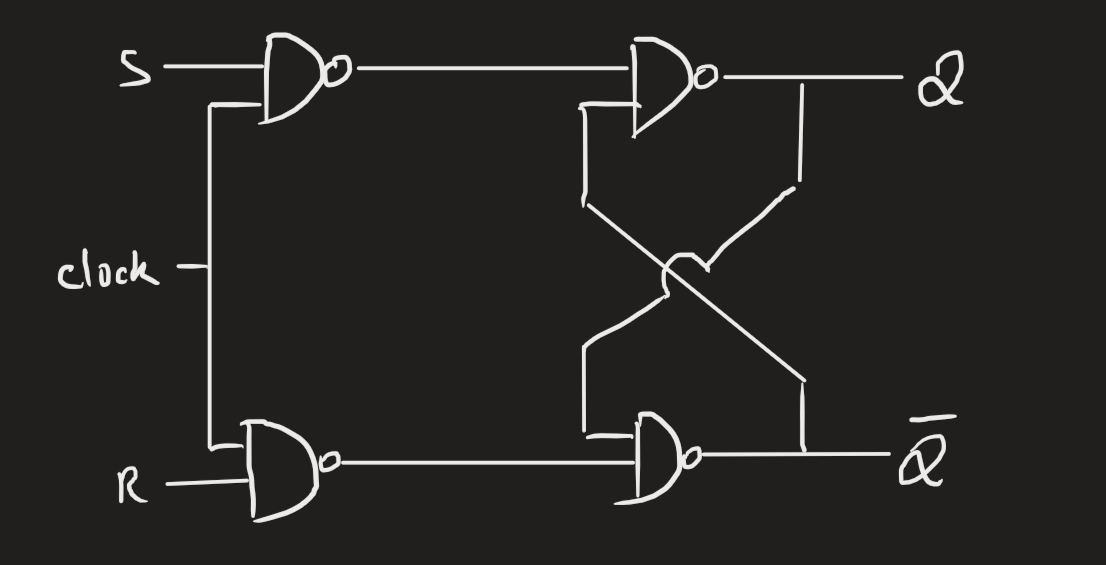

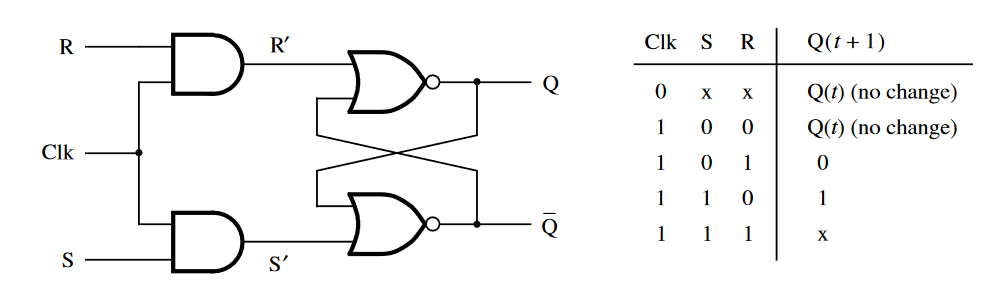

Gated SR latch

Gated SR latches add a clock that can be used to disable and enable the effects of and . If the clock is 0, then (the memory state).

It’s pretty typical to express gated RS latches only with NAND.

Simple case

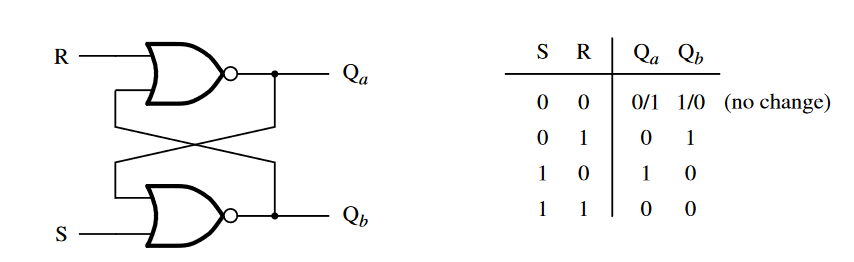

Our simplest case are simple SR latches:

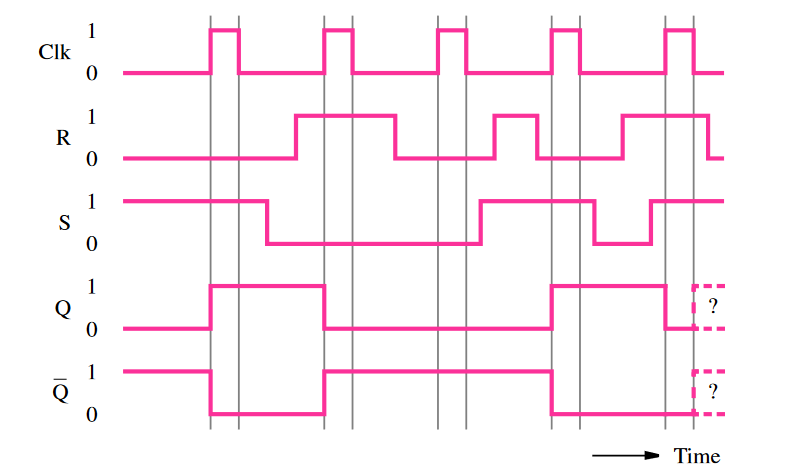

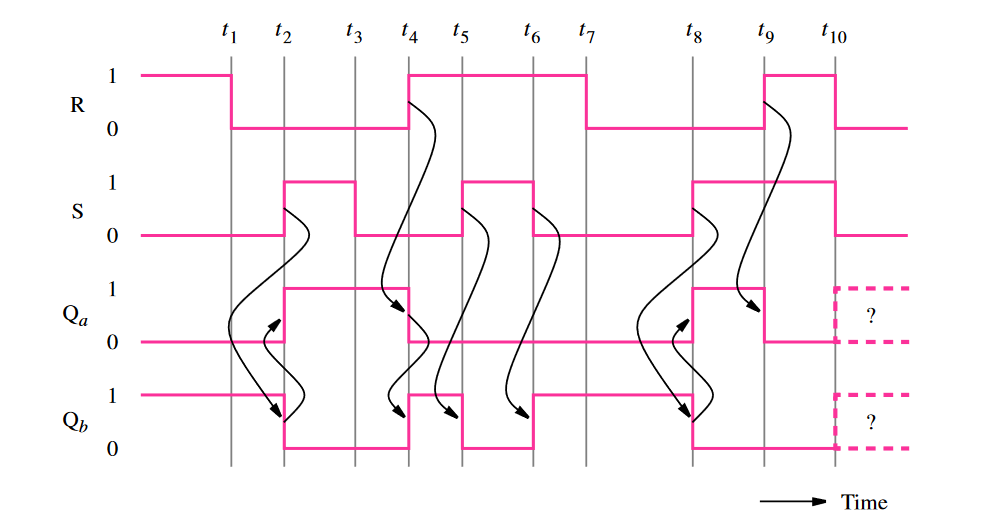

Observe that for , , we get oscillations in and , making this circuit difficult and inadvisable to use.

Observe that for , , we get oscillations in and , making this circuit difficult and inadvisable to use.

See also

- D-latch and flip-flops