A multiplexer (mux) is a broad type of logic circuit that takes multiple data inputs and selector inputs. They’re best analogous to conditional statements in programming — if we meet a certain condition, then we select certain data to pass through.

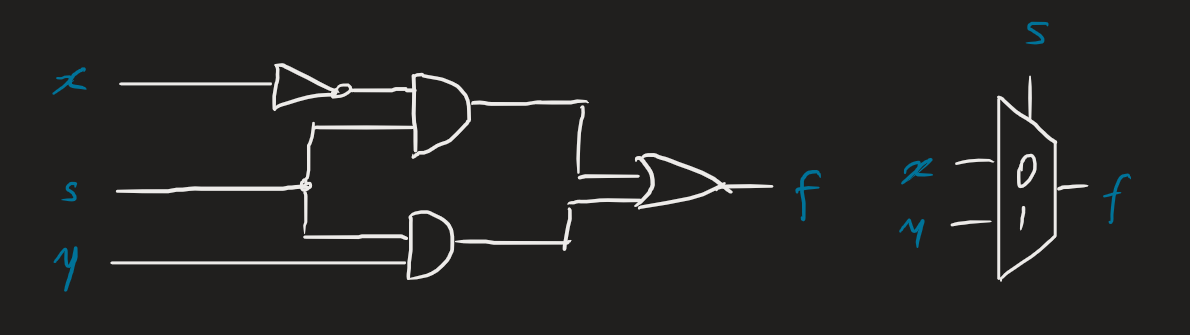

Multiplexers can be huge if necessary. A basic 2-to-1 multiplexer is given by the expression:

We can extend to a 2-bit wide gate:

And so on.

Implementation

In Verilog, multiplexers can be explicitly defined with their logic expressions, or we can use case statements to achieve the same effect.

Explicitly, we can implement a two-bit wide multiplexer in Verilog as a combination of two one-bit wide multiplexers (this holds for higher-order wide multiplexers).

module mux2to1(x, y, s, m);

input x, y, s;

output m;

assign m = (~s & x) | (s & y);

endmodule;

module mux2to1_2bit(x, y, s, m);

input s;

input [1:0] x, y;

output [1:0] m;

mux2to1 unit_0 (x[0], y[0], s, m[0]); // invokes the module above

mux2to1 unit_1 (x[1], y[1], s, m[1]); // order doesn't matter! not sequential

endmodule;With case statements:

always@(*) begin

case(select)

2'b00: // something

2'b01:

2'b10:

2'b11:

default:

endcase

end