https://github.com/standardsemiconductor/riscv-formal

RISC-V is an open source RISC instruction set architecture, configurable for a large range of applications, including 32-bit and 64-bit.

By default, RISC-V has 32-bit words, and may support 64-bit doublewords with proper extensions.

Extensions

What makes RISC-V so versatile are extensions that define additional registers and instructions for extra functionality. This includes:

- Base integer instructions: RV32I, RV64I

- Multiplication: RV64M

- Floating-point operations: RV64F and RV64D (for double precision)

- Atomics: RV64A

- Vector operations: RV64V

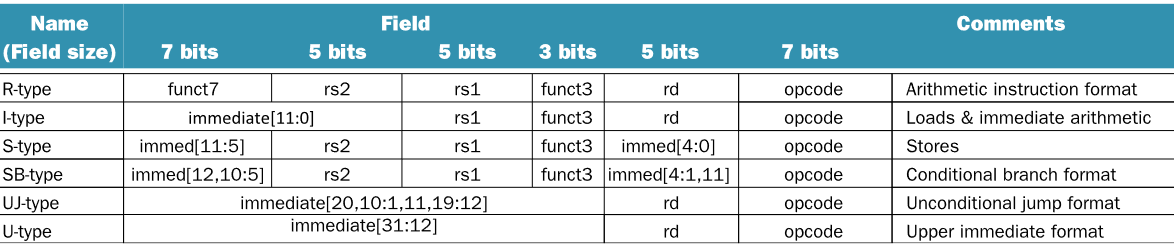

All RISC-V instructions are 32-bits. Because of this restriction, we have several types of instructions with different machine code formats.

- R-type — operates solely on registers. These have three register operands.

- I-type — operates with immediate and load instructions.

- S-type — operates with store instructions.

This chart describes the instruction formats:1

In SystemVerilog:

In SystemVerilog:

typedef struct {

logic[6:0] funct7;

logic[4:0] rs2;

logic[4:0] rs1;

logic[2:0] funct3;

logic[6:0] rd;

logic[6:0] opcode;

} instr_r;Instructions

Flow control and functions:

- Jumps

jal xn, Imm32to unconditionally branch and save the address of the instruction to the destination registerrd.jalr x1, 0(x2)for jump-and-link register. This essentially does the unconditional branch to the address specified in a register.

Registers

Data is operated on within 32 base registers, between x0 and x31. Some specialised registers:

x0will only store'b0.x1is a return address to the point of origin.x2/spis the stack pointer.x3/gpis reserved by some compilers for the global pointer, for access to static data.

We also follow a convention in our code where:

x10-x17are parameter registers to pass parameters or return values.x5-x7andx28-x31are temporary registers that aren’t preserved by the function callee.x8-x9andx18-x27are saved registers that are preserved on a function call (if used, the callee saves and restores them).

At start-up time, all registers should be assumed to be uninitialised.

Addendums

Prof Anderson notably thinks that RISC-V is going to be vastly more popular than ARM or x86 in the future. He points to open source software in the compiler space (GCC, G++) that essentially ended the use of commercial compilers in the software industry that were prevalent around the 90s and 00s, suggesting that the same thing may happen in the hardware industry with ARM (commercial) and RISC-V.

Tenstorrent is betting hard on RISC-V being the future.

Resources

- Computer Organization and Design: RISC-V Edition, by David A. Patterson and John L. Hennessy

- Official specifications, as of 11 April 2024

See also

Footnotes

-

From Computer Organization and Design: RISC-V Edition by Hennessy and Patterson. ↩