In Verilog, we have assignment operators, similar to any other HDL or programming language. The difference is that we have two kinds of basic assignment operators: a blocking and non-blocking assignment.

A <= B; // non-blocking

A = B; // blockingThe blocking assignment operates functionally similar to many programming languages. The assignment cannot happen until the previous line’s operation has completed, if the assignment depends on the previous line. Earlier statements can affect later statements.

The non-blocking assignment evaluates all actions at once. This is especially applicable within an always block when dealing with sequential circuits. Using the blocking operator can lead to odd synthesis of circuits and unexpected behaviour.

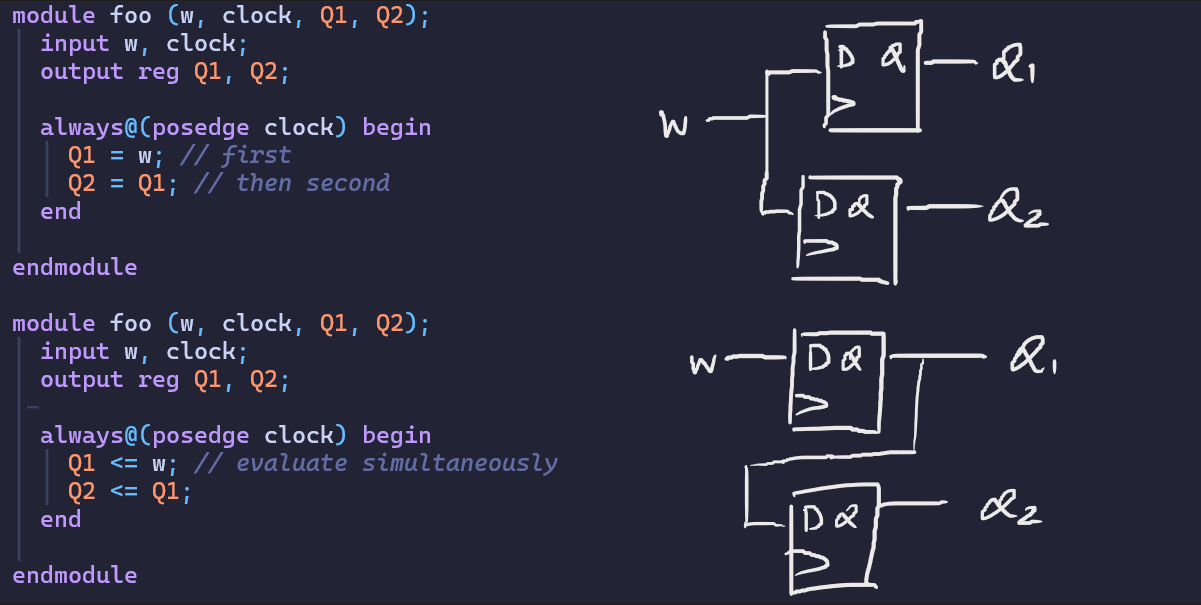

Take this example. In the first example, we have the use of blocking assignments. In the second, we have the use of non-blocking assignments. Observe the differences in the synthesised circuits.