Counters are digital circuits that increment or decrement by 1, often used in conjunction with a button that we press to change the value of our counter.

HDL implementation

Say we want an active-low parallel load loadn, and an asynchronous active-low reset resetn.

module count8 (clock, loadn, resetn, Q, D);

input clock, resetn, loadn;

input [7:0] D;

//..

always@(posedge clock, negedge resetn)

begin

if (resetn == 1'b0)

Q <= 'b0;

else if (loadn == 1'b0)

Q <= D;

else

Q <= Q + 1'b1;

end

endmoduleUnder the hood

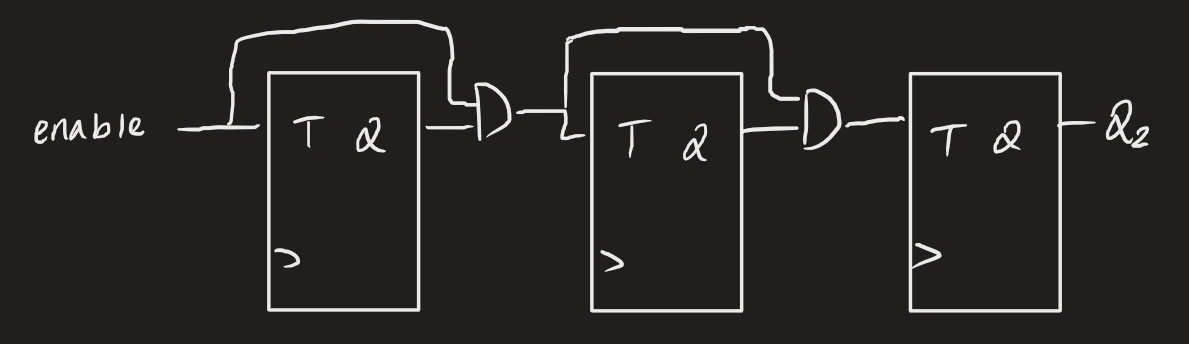

Under the hood, counters are implemented with T flip-flops. We may add additional logic to only change the value if a signal is passed through (i.e., a button is pressed). Consider this 3-bit up-counter schematic:

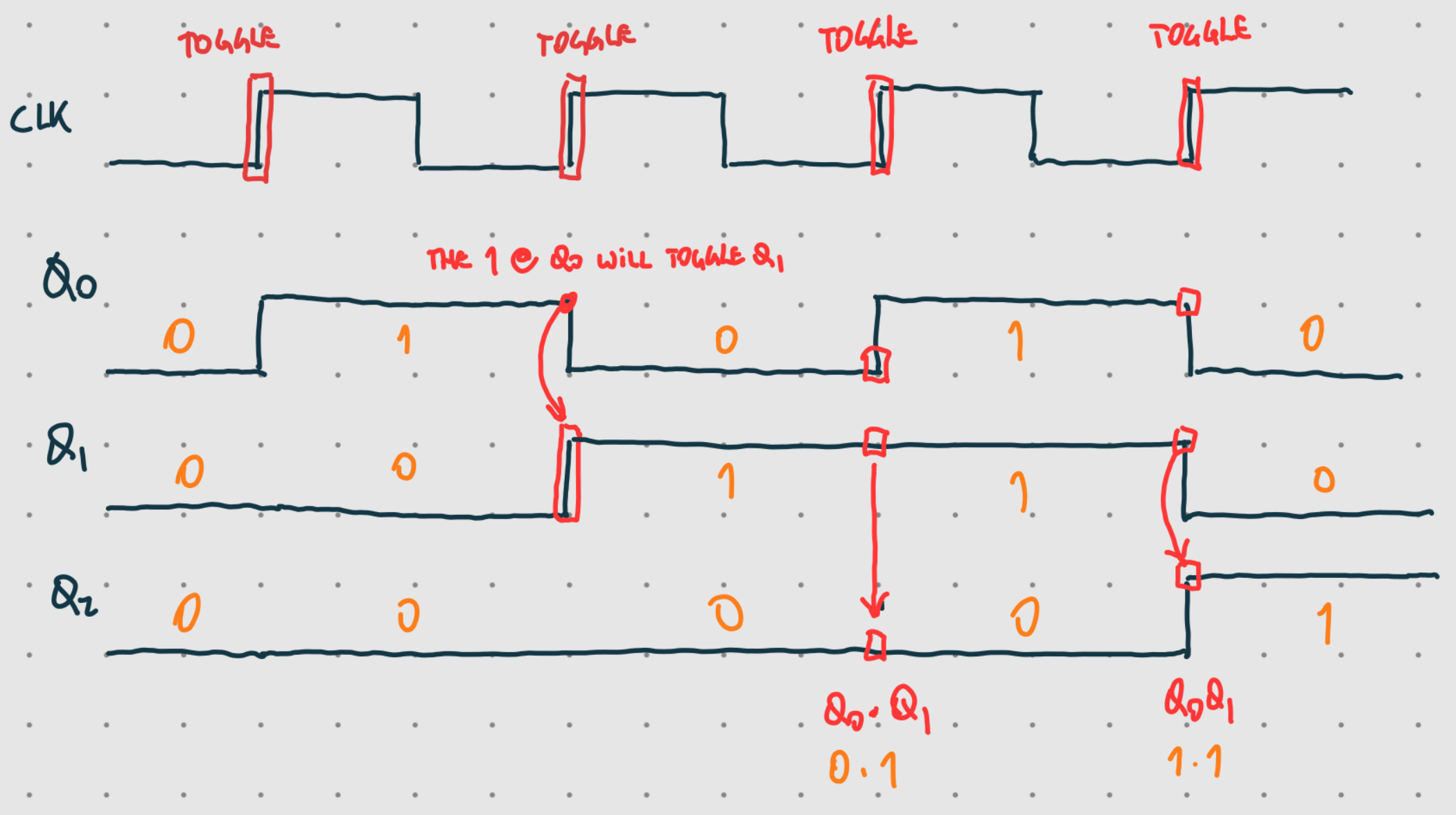

Here’s a sample timing diagram:1

Here’s a sample timing diagram:1

See also

- Rate divider, which uses counters

Footnotes

-

From Prof Korst’s lecture notes. ↩